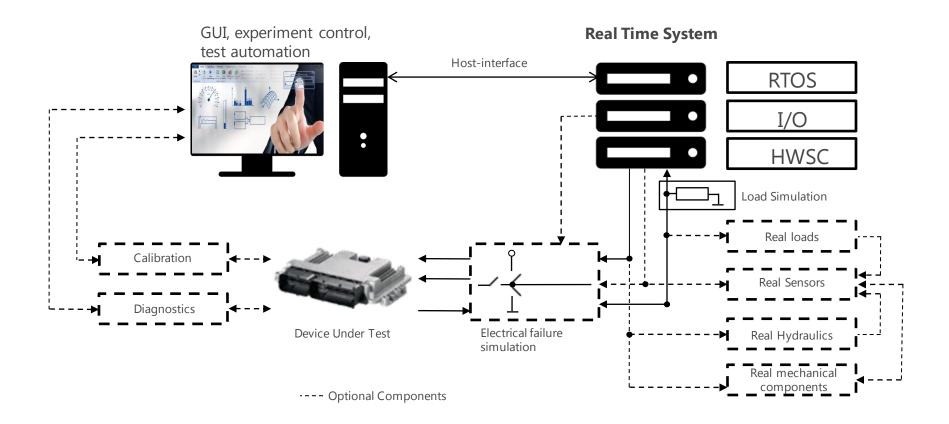

# **System Introduction**

# **Goals and Advantages of the HIL-Simulation**

### Goals of the HIL-simulation

- Increased productivity (higher coverage of potential test cases)

- Reduction of development cost (less test benches and prototype vehicles)

- Coping with increased complexity

## **Advantages of HIL-tests**

- Function tests in early development stages

- HIL-tests can be reproduced and automated

- Certain test are not possible or too dangerous with a real system

- HIL-tests give the possibility to reproduce a certain error condition (diagnostic tests, emergency run programs, fall-back programs)

## **Basic Considerations for E-Drive Simulation**

#### **Drive physics**

Characteristic

Dependencies (current,

position, temperature, ...)

Motor Type (PMSM, IM, ...)

Motor Commutation (sinusoidal, trapeziodal, ...)

#### **Simulation Level**

Signal, Power or Mechanical level

#### **Real-Time Platform**

Target Real-Time Platform (Processor, FPGA) Sampling Startegy (synchronized, oversampling)

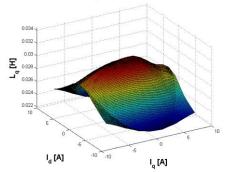

#### **Simulation Model**

Mathematical Approach (equation, maps, statespace)

Coordinate System (a/b/c,  $\alpha/\beta$ , d/q)

Parameter (characteristic data or maps)

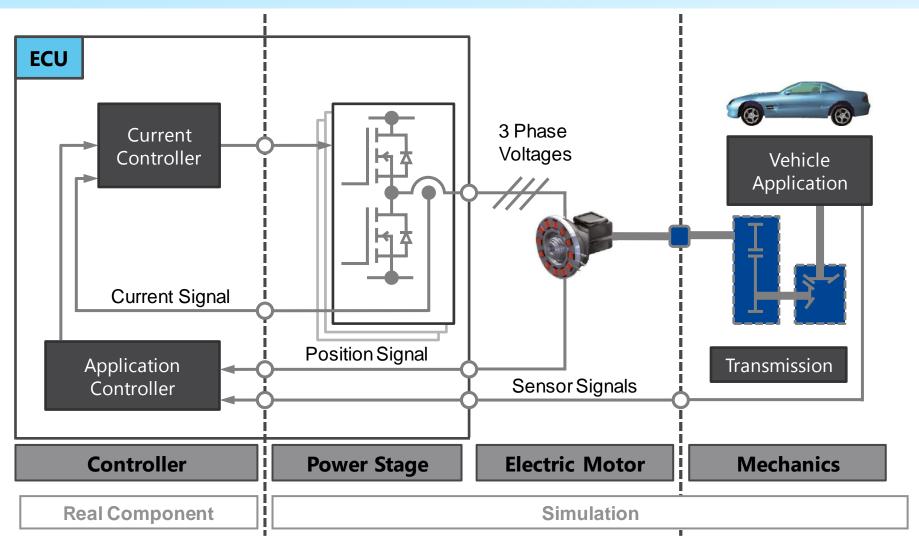

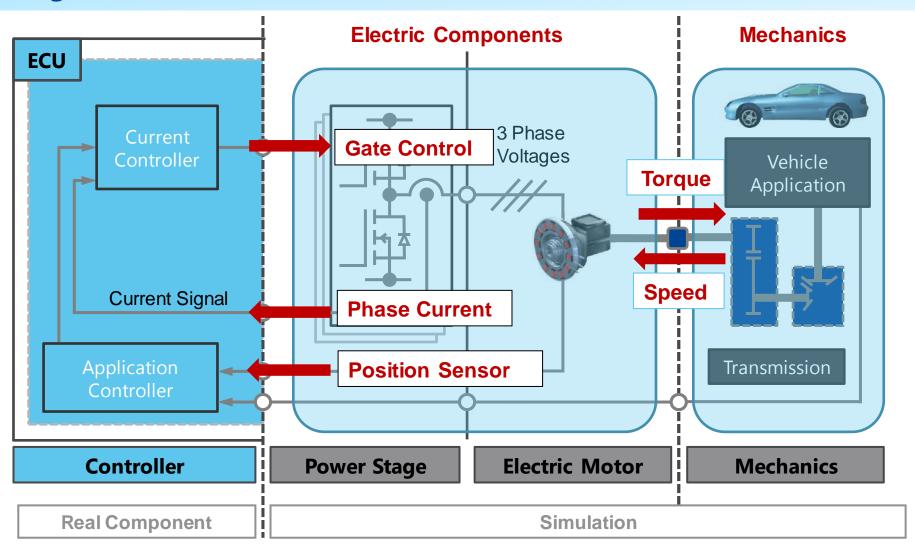

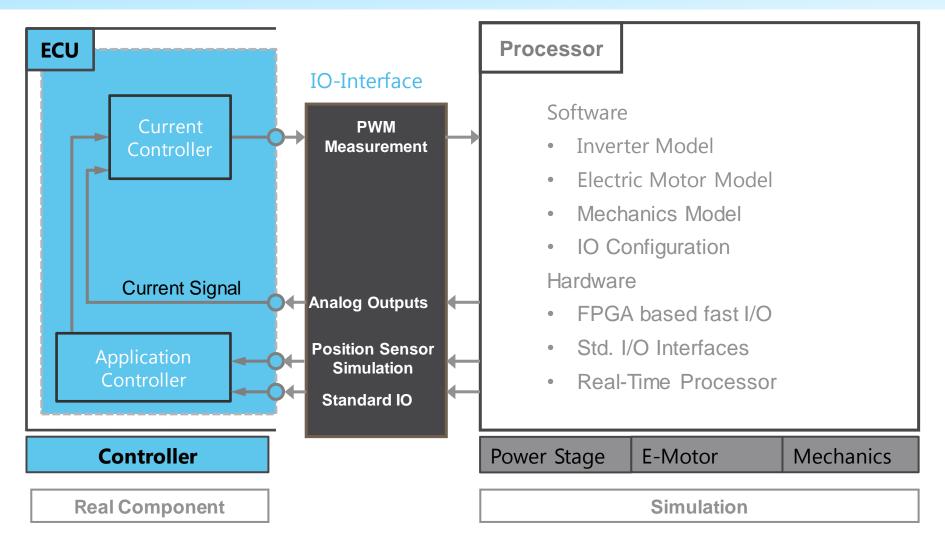

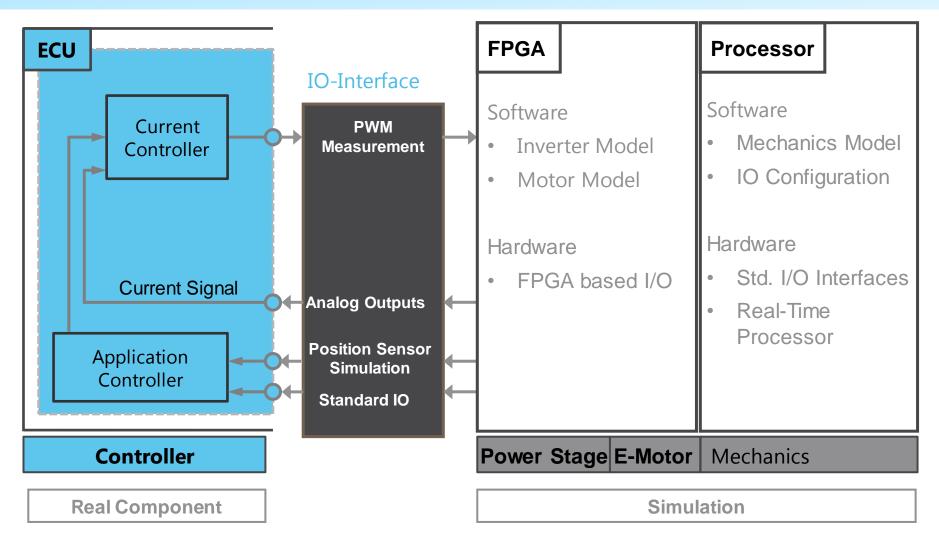

## **Interfaces for Simulation of e-drive**

# **Signal Level Simulation**

## **Preconditions for Simulation on Signal Level**

- Internal Signals of the ECU have to be accessible

- Current Sensor Feedback Signals (e.g. ADC that measures the HALL transduced feedback

- Power Electronic Control Signals (e.g. Gate Driver PWM signals)

## **Preconditions for Simulation on Signal Level**

## Internal Signals of the ECU have to be accessible

- Current Sensor Feedback Signals (e.g. ADC that measures the HALL transduced feedback

- Power Electronic Control Signals (e.g. Gate Driver PWM signals)

#### Processor based Simulation

- For Drives that operate at low switching frequencies, typically 16-20kHz

- Running at moderate frequencies (< 2kHz electric fundamental frequency)</li>

- The additional delay of the average model can be neglected

# **Preconditions for Simulation on Signal Level**

## Internal Signals of the ECU have to be accessible

- Current Sensor Feedback Signals (e.g. ADC that measures the HALL transduced feedback

- Power Electronic Control Signals (e.g. Gate Driver PWM signals)

#### Processor based Simulation

- For Drives that operate at low switching frequencies, typically 16-20kHz

- Running at moderate frequencies (< 2kHz electric fundamental frequency)</li>

- The additional delay of the average model can be neglected

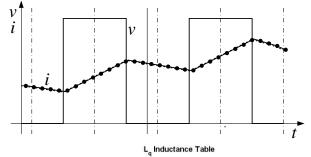

### FPGA based Simulation

- For Drives that operate at higher switching frequencies

- Are running at high frequencies

- A quasi continuous current simulation is required for the control algorithms of the DUT

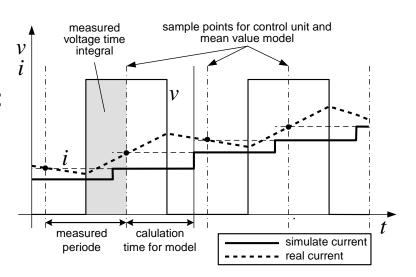

### **Processor based E-drive Simulation**

## Advantages

- Sampling frequency is usually same as switching frequency of the ECU (Sometimes oversampling by a factor 2 or 4 possible)

- Mean value models are sufficient

- Full traceability of internal model signals

- Simulation in a well known environment

## Disadvantages

- Synchronized model Calulation required

- Limited electric fundamental frequency

- Limited range of switching frequency

- Mean value current output with delay

- High computation load on processor

## **Processor based E-drive Simulation**

## **FPGA based E-Drive Simulation**

## Advantages

- Sampling frequency is much higher than switching frequency of the ECU

- Quasi-continuous current output without delay (Simulation of PWM effects)

- Control of Electronic loads possible

- Wide range of switching frequency

- High electric fundamental frequency

- Low computation load on processor

- Non linear effects such as spatial harmonics

## Disadvantages

- Limited topology size per FPGA

- No tracability of internal model signals by default

## **FPGA based E-Motor Simulation**

# **Questions**