# VERIFICATION AND VALIDATION TECHNIQUES FOR I&C APPLICATIONS IN NORDIC NPPS

REPORT 2016:268

# Verification and validation techniques for I&C applications in Nordic NPPs

SAMUEL GEORGE, SOFIA GUERRA AND CATHERINE MENON, ADELARD LLP

ISBN 978-91-7673-268-7 | © 2016 ENERGIFORSK Energiforsk AB | Phone: 08-677 25 30 | E-mail: kontakt@energiforsk.se | www.energiforsk.se

### Foreword

This report is produced by Adelard LLP for Energiforsk within the research program ENSRIC, Energiforsk Nuclear Safety Related Instrumentation and Control systems. The objective of the project was to develop an understanding of the verification and validation aspects of safety related systems built on FPGA-technology (Field Programmable Gate Arrays) for nuclear applications.

FPGAs have been gaining interest from the nuclear industry for a number of years, but lately they have been questioned and the initial hypothesis that the technology would be easier to license compared to microprocessor-based platforms for nuclear applications is now questioned. This report is the second ENSRIC report on FPGA:s, and it is focused on verification and validation and standards of FPGAs compared to what is applied to microprocessor-based systems. The previous report is named "Field Programmable Gate Arrays in safety related instrumentation and control applications", Energiforsk report 2015:112.

ENSRIC is focused on safety related I&C systems, processes and methods in the nuclear industry. The three focus areas of the program are

- LTO of existing analogue platforms

- Asset management of existing digital platforms

- Emerging technologies.

The ENSRIC results are used in the plant development process, including managers, strategic teams, analysts and implementation teams at the NPPs and at the authorities, to contribute to safe and robust I&C systems that promotes low Life Cycle Cost. The program is financed by Vattenfall, Uniper, Fortum, TVO, the Swedish Radiation Safety Authority, Skellefteå Kraft and Karlstad Energi.

# Sammanfattning

#### Den här rapporten beskriver metoder för verifiering och validering av mikroprocessorer och FPGA. Den lyfter fram metoder som är tillämpliga för dem bägge men även några som är specifika för var och en av dem.

För varje metod redogörs för dess relativa effektivitet och dess förmåga att bidra till den övergripande konfidensen på ett I&C-systems egenskaper, som utför Cat Afunktioner. Olika metoder för V&V har jämförts med hjälp av ett trefaldigt angreppssätt, som har visat sig vara effektivt vid genomförandet av en säkerhetsdemonstration. Angreppssättet beaktar på ett systematiskt sätt bidragen från kända standards, analys av beteendeegenskaper samt sårbarheter som vanligen kopplas samman med specifika teknologier och typer av design

I den komparativa analysen av olika standarder, har skillnader mellan olika relevanta IEC standarders krav på V&V, genom alla faser i livscykeln, undersökts. De signifikanta skillnader som identifierades var väldigt få. Generellt sätt kan säga att den relevanta FPGA standarden är mindre föreskrivande/normativ med avseende på vilka specifika dokument som behöver tas fram. I vissa fall görs klargöranden genom hänvisning till den motsvarande standarden för mikroprocessorer. Dessa klargöranden ställer inte krav på utförande av specifika aktiviteter utan detaljerar snarare vilka andra standarder som kan tillämpas vid specifika förhållanden. Den relevanta FPGAstandarden har också undvikit vissa av tvetydigheterna som återfinns i den relevanta standarden för mikroprocessorer.

Vid undersökning av V&V-metoderna som kan användas för att åstadkomma korrekt beteende visade det sig att många är desamma eller likartade. Särskilt snarlika är angreppssätten för dynamisk testning på systemnivå. För vissa tidsparametrar, såsom responstid och samtidighet, krävs dock olika angreppssätt. Det beror på att FPGA i grunden är en parallell modell medan mikroprocessorer är sekventiella och naturen hos de frågeställningar på den fysiska nivån som måste beaktas vid FPGA utveckling (frågeställningar som en programmerare av mikroprocessorer kan bortse ifrån). FPGA verktyg är generellt sett mycket mer sofistikerade i sitt sätt att stödja V&V jämfört med vanliga programmeringsverktyg. FPGA-verktygens ökade komplexitet är nödvändig för att kompensera för den ökade komplexiteten hos FPGA. Vid FPGA-utveckling finns ett antal frågeställningar kring elektronikdesign som behöver tas omhand, som faller inom kortdesignerns ansvarsområde i fallet med mikroprocessorer. På grund av den naturliga ensidigheten hos HDL verktyg vid hårdvaruutveckling på låg nivå kan det vara nyttigt med ytterligare kontroll av V&V aktiviteter avseende beteenden hos FPGA baserade system för att jämföra täckningsgraden för egenskaper som visar korrekt beteende på olika abstraktionsnivåer med motsvarande metoder som skulle använts vid V&V av en motsvarande mikroprocessorimplementering för samma applikation.

Metoderna för V&V som riktar sig till att analysera sårbarheten i implementeringar av FPGA respektive mikroprocesser, skiljer sig åt betydligt på grund av de radikalt olika fysiska egenskaperna och hårdvarans designparametrar och berör oftast inte systemets beteende som "svart låda". Många av de svårbehandlade sårbarheterna i ett mikroprocessorbaserat system så som osäkerhet kring påverkan från avbrottshanteringen på interaktionen mellan uppgifter och övergripande systemprestanda saknas vid implementering av FPGA. Många av osäkerheterna relaterade till avbrott är en konsekvens av operativsystemets växlande mellan olika

uppgifter och dess resurshantering. Operativsystems baskod är också en källa till sårbarhet eftersom den oftast är utvecklad i förväg och består till en viss del av kod vars tillförlitlighet är svår att fastställa. Omsorg måste vinnläggas om att för att lindra bristen på transparens i koden som slutligen laddas upp i FPGA. Likaledes behöver frågeställningar kring dataflöden och kontrollflöden på hög abstraktionsnivå hanteras, där HDL statisk analys inte nödvändigtvis behöver tillföra god täckningsgrad.

Kortfattat, vid jämförelse av V&V genom dessa tre olika områden, har det identifierats få systematiska skillnader bland de aktiviteter som erfordras för mikroprocessorer och FPGA baserade system. Metoderna som behövs på de lägre nivåerna är olika och kräver olika typer av expertis. För FPGA gäller i många fall att angreppssättet är mer omfattande men det är viktigt att utvärdera hela uppsättningen av de V&V –metoder som använts i varje enskilt fall för att försäkra sig om att alla nivåer i konstruktionen och implementeringen är tillräckligt täckt , speciellt om den slutliga bedömningen har gränsytor mot ett annat system som har utvecklats eller utvärderats av ingenjörers som är mer bekanta med V&V processer för mikroprocessorbaserade system. Förutvecklade komponenter, så som IP-kärnor för FPGA och operativsystem för mikroprocessorer, är viktiga aspekter att ta hänsyn till vid säkerhetsbedömning av alla I&C-system. Medan IP-kärnor kan undvikas (och de är ofta förbjudna i system som utför Cat A funktioner) kräver säkerhetsbedömning av operativsystem för mikroprocessorer en ansenlig mängd V&V-aktiviteter.

### Summary

#### This report considers the verification and validation techniques that can be applied to microprocessors and FPGAs, highlighting techniques that are similarly applicable to both, and those that are specific to a particular platform architecture.

In each case, the relative effectiveness of these techniques and their contribution to the overall level of confidence of an instrumentation and control (I&C) system performing a Cat A function is considered. We have compared verification and validation (V&V) techniques using a threefold approach that we have found to be effective in achieving a safety justification. This method systematically considers the contribution of recognised standards, analysis of behavioural properties, and vulnerabilities that are commonly associated with particular technologies and design approaches.

In our comparative analysis of standards we looked for differences in V&V requirements in relevant IEC standards at all stages of the development lifecycle, and found very few significant differences. In general, the relevant FPGA standard is less prescriptive about the specific documents that need to be produced. In some cases it has clarified requirements in the equivalent microprocessor standard. These clarifications have typically not taken the form of requiring that specific activities be performed, but have given more detail on the applicability of other standards in various circumstances and have avoided some ambiguities that are present in the relevant microprocessor standard.

In examining the V&V techniques applicable to establish correct behaviours, we found that many are the same or similar. In particular, many of the system level dynamic testing approaches are identical. However, timing and concurrency require different approaches. This is a consequence of the fundamentally parallel model of an FPGA in contrast to a sequential microprocessor and the nature of the issues at the physical level that need to be considered in FPGA development (which a microprocessor programmer can neglect). FPGA tools are generally much more sophisticated in the V&V support they provide when compared to ordinary programming tools, but some of this additional complexity is necessary in order to compensate for the additional complexity of FPGAs, which must deal with a number of electronic design automation issues that are the province of the chip designer in the microprocessor case. Owing to the natural bias of HDL tools to low level hardware development, it may be a useful additional check in V&V activities for the behaviours of an FPGA based system to compare the coverage of correctness properties at different levels of abstraction with the analogous techniques that would be used in the V&V for an equivalent microprocessor implementation of the same application.

V&V techniques to address vulnerabilities in FPGA and microprocessor implementations vary considerably owing to the radically different physical properties and design parameters of the hardware, and do not generally concern the black box behaviour of a system. Many of the most intractable vulnerabilities in microprocessor based systems, such as lack of certainty about the impact of interrupts on task interaction and overall system performance, are absent in FPGA implementation flows. Many of the uncertainties relating to interrupts are a consequence of the operating system's task switching and arbitration between resources. The code base of the operating system itself is also a source of vulnerabilities, since it is usually pre-

developed and may amount to a significant amount of code whose reliability is often difficult to establish. However, care must be taken to mitigate the lack of transparency in the code artefacts that are eventually uploaded to the FPGA, as well as any data flow or control flow issues at a high level of abstraction, of which HDL assertion checking techniques do not necessarily provide good coverage.

Overall, in our comparison of V&V through these three separate lenses, we have found few systemic differences in the activities required for microprocessor and FPGA based systems, but the lower level techniques needed are different and require different types of expertise. In many cases, for FPGA techniques, the approach is more comprehensive, but it is important to review the whole suite of V&V techniques used in any particular case to ensure that all levels of design and implementation are adequately covered, particularly if the resulting justification must interface with another case that has been developed or reviewed by engineers more familiar with microprocessor based V&V processes. Pre-developed components such as IP cores for FPGAs and microprocessor operating systems are an important aspect of assuring any I&C system; while IP cores may be avoided (and are often prohibited for systems performing Cat A functions), the assurance of microprocessor operating systems will require a considerable amount of V&V activity that would need to performed.

# List of content

| 1 | Introd | duction                                              | 12 |

|---|--------|------------------------------------------------------|----|

| 2 | Backg  | round                                                | 13 |

| 3 | Stand  | ards compliance                                      | 15 |

|   | 3.1    | Methodology                                          | 15 |

|   | 3.2    | IEC 60880                                            | 15 |

|   | 3.3    | IEC 62566                                            | 17 |

|   | 3.4    | Results                                              | 17 |

|   |        | 3.4.1 Requirements phase                             | 18 |

|   |        | 3.4.2 Design and implementation phase                | 18 |

|   |        | 3.4.3 Verification                                   | 19 |

|   |        | 3.4.4 Software / HPD aspects of system integration   | 20 |

|   |        | 3.4.5 Software / HPD aspects of system validation    | 21 |

|   |        | 3.4.6 Modification                                   | 21 |

|   |        | 3.4.7 Software tools for development                 | 21 |

|   |        | 3.4.8 Acceptance of pre-developed products           | 21 |

|   | 3.5    | Conclusions                                          | 22 |

| 4 | Behav  | vioural properties                                   | 23 |

|   | 4.1    | Functionality                                        | 23 |

|   | 4.2    | Timing                                               | 26 |

|   |        | 4.2.1 Worst case execution time                      | 28 |

|   |        | 4.2.2 FPGA static timing issues                      | 29 |

|   | 4.3    | Accuracy                                             | 29 |

|   | 4.4    | Availability                                         | 30 |

|   | 4.5    | Robustness                                           | 31 |

|   | 4.6    | Fault tolerance, diagnostics and failure recovery    | 31 |

|   | 4.7    | Conclusions                                          | 32 |

| 5 | Vulne  | rability assessment                                  | 33 |

|   | 5.1    | Equivalence between design and implementation levels | 33 |

|   | 5.2    | Timing vulnerabilities                               | 35 |

|   |        | 5.2.1 Microprocessors                                | 36 |

|   |        | 5.2.2 FPGAs                                          | 36 |

|   |        | 5.2.3 Comparison summary                             | 37 |

|   | 5.3    | Initialisation                                       | 38 |

|   | 5.4    | High level code or HDL bugs                          | 38 |

|   | 5.5    | Incorporation of third party code                    | 38 |

|   | 5.6    | Unrevealed implicit state corruption                 | 39 |

|   | 5.7    | Silicon design errors                                | 40 |

|   | 5.8    | Microprocessor vulnerabilities absent in FPGAs       | 41 |

|   | 5.9    | Vulnerabilities – conclusions                        | 41 |

| 6 | FPGA t  | echnology-specific issues                                                       | 43 |

|---|---------|---------------------------------------------------------------------------------|----|

|   | 6.1     | SRAM                                                                            | 43 |

|   | 6.2     | Antifuse                                                                        | 43 |

|   | 6.3     | Flash                                                                           | 43 |

|   | 6.4     | Modules, mezzanine cards, backplanes and communication between chassis or racks | 44 |

| 7 | Conclu  | sion                                                                            | 45 |

| 8 | Glossa  | ry                                                                              | 46 |

| 9 | Bibliog | raphy                                                                           | 47 |

## 1 Introduction

This report considers the verification and validation (V&V) techniques that can be applied to microprocessors and FPGAs, highlighting techniques that are similarly applicable to both, and those that are specific to a particular platform choice. In each case, the relative effectiveness and the contribution of these techniques to the overall level of confidence of an instrumentation and control (I&C) system performing a Cat A function is considered. Section 2 introduces the project context and approach. Section 3 considers similarities and differences between the V&V requirements of standards for each of the architectures. Section 4 similarly examines V&V techniques needed to establish particular facets of I&C behaviour, while Section 5 does the same for design and implementation vulnerabilities. Section 6 considers issues particular to different FPGA types. Section 7 concludes. Section 8 gives the abbreviations used and Section 9 is a list of references.

# 2 Background

Field Programmable Gate Arrays (FPGAs) have been gaining interest from the nuclear industry for a number of years. Their simplicity compared to microprocessor-based platforms is expected to simplify the licensing approach, and therefore reduce licensing risks compared to software-based solutions.

Although the use of an FPGA can result in a final product that is hardware only, with no run-time software, the process used to develop the application is software-intensive, using advanced software tools to design, implement and verify the application. In both cases there is a process of specification, coding and compilation (even if different languages and tools are used). We would therefore expect the approaches taken for justifying software-based systems to be broadly similar to the justification of FPGA applications. Indeed, there is a growing international consensus that the regulatory review of FPGA-based systems should treat the application development process in a manner similar to software development, invoking many of the same standards and guidelines that are used for software-based systems, with some adaptation.

There has been a number of applications of FPGAs in the nuclear industry, such as the Main Steam and Feedwater Isolation System at Wolf Creek plant, in the US (class 1E), and a number of safety applications including Reactor Trip Systems (RTS) for 4 Nuclear Power Plants (NPPs) in Ukraine (24 systems), Engineering Safety Features Actuation Systems (ESFAS) for 5 NPPs in Ukraine and Bulgaria (18 sets) and Reactor Power Control and Limitation System (RPCLS) for 4 NPPs (8 systems). A number of applications are planned for new builds. These applications were developed prior to the publication of IEC 62566 [6]. For most of the applications in the nuclear industry, there was no specific FPGA guidance or standard for the development and justification of FPGAs in nuclear applications. The approach taken was to adapt software regulations and standards to the context of FPGAs.

During 2014, we worked on a project with the objective of developing an overview of the position of safety-related systems built on FPGA technology for nuclear applications. This investigated if FPGA-based systems were a realistic alternative in future investment programs in the Nordic NPPs within the next 5 years, considering technological advancement, licensing, market situation etc. The conclusion was that FPGAs may have a role in future modernisation of I&C systems in Sweden.

This project is a continuation of the work performed in 2014. Its objective is the evaluation of the V&V activities that are necessary to implement an FPGA-based application and compare them with equivalent activities to assess a microprocessor-based solution.

This study reviews the V&V activities that are needed to implement an application in an FPGA based product and compares it with what might be equivalent for a microprocessor based application. Different activities have different objectives in terms of assurance, and will achieve different levels of confidence in the system. In order to be able to perform this comparison, it is necessary to define criteria. We base our overall approach on a comparison of different aspects of a safety demonstration so that similar levels of assurance can be achieved across the different architectures. This is done considering

• the verification and validation activities required by relevant standards (Section 3)

- verification and validation activities to achieve confidence that all behavioural properties have been met (Section 4)

- verification activities to ensure that typical vulnerabilities of the technologies have been avoided (Section 5)

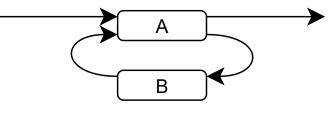

This approach considers the three aspects of assurance that we usually describe as *the strategy triangle of justification* [3], which is described in more detail in Appendix D.

Figure 1: The strategy triangle of justification

The focus of this project is on safety functions, or those categorised as Cat A according to IEC 61226 [2], and on "small and medium size applications". It does not cover large applications where several FPGA based units communicate with each other via networks or communication links (although several of the issues would be similar). When practicable, we indicate tools that are available to support the activities.

# **3** Standards compliance

This section summarises our findings from reviewing the V&V activities required by comparable standards for FPGA-based and software-based I&C systems performing Cat A functions. The standards chosen were IEC standards, with IEC 60880 [4] being selected for software systems and IEC 62556 [6] for FPGA-based systems.

#### 3.1 METHODOLOGY

To identify the differences for discussion, we first performed a comparison review of the two standards. As the prescribed development methodologies share many commonalities (Figure 3 and Figure 4), we began by looking at each distinct lifecycle phase. It is important to note that this was a semantic review and comparison as opposed to a syntactic examination; we have identified only those differences that impact the development activities, rather than cosmetic differences.

In each case where a difference was identified, we assessed this for its potential impact on the V&V activities. In some cases we considered that there would be no impact, and therefore have not taken this further in this report. Where we consider that there is a potential impact on V&V activities, we have identified this and its potential effects in Section 3.4.

#### 3.2 IEC 60880

The scope of IEC 60880 is to provide requirements for the software aspects of computer-based I&C systems performing Cat A functions in nuclear power plants. It was first issued in 1986 and has since been re-issued a number of times to take into account the changing practices and techniques of software engineering.

IEC 60880 is directly referenced by IEC 61513 [5], which focuses on general requirements for I&C systems performing functions important to safety in NPPs. IEC 60880 is also associated with IEC 62138, which covers computer-based I&C systems performing category B and C functions.

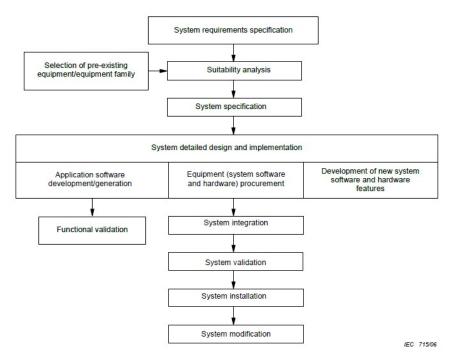

IEC 60880 assumes a system safety lifecycle equivalent to that discussed in IEC 61513, and shown in Figure 2.

Figure 2: System safety lifecycle from IEC 61513 [5]

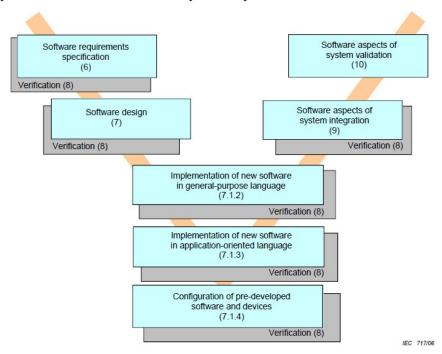

IEC 60880 refines this further to identify a software development lifecycle making use of distinct phases. This is shown in Figure 3. As can be seen, each separate lifecycle phase involves verification of the phase outputs.

Figure 3: Software development lifecycle from IEC 60880

#### 3.3 IEC 62566

The scope of IEC 62566 is to provide requirements for the use of HDL-programmed devices (HPDs) in I&C systems performing Cat A functions in nuclear power plants. It was first issued in 2012 and has not been re-issued since.

IEC 62566 references IEC 61513 [5], which focuses on general requirements for I&C systems performing functions important to safety in NPPs. IEC 62566 is intended to be used in conjunction with IEC 60987, which covers generic hardware design issues, and with IEC 60880 for aspects of the development when the HPD and software issues are identical.

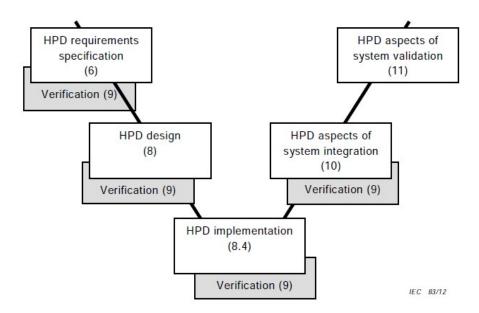

Like IEC 60880, IEC 62566 assumes a system safety lifecycle equivalent to that discussed in IEC 61513, and shown in Figure 2. The HPD development activities as described by IEC 62566 also follow a V-model very similar to that in IEC 60880, as shown in Figure 4.

Figure 4: HPD development lifecycle from 62566

#### 3.4 RESULTS

Overall, there are very few significant differences in terms of V&V requirements imposed by IEC 60880 and IEC 62566. The two major differences that we found were firstly, that IEC 62566 is generally more goal-based and less prescriptive about how the results of the difference activities have to be recorded and secondly, that some of the ambiguities in phrasing in IEC 60880 have been clarified in the more recent IEC 62566.

IEC 62566 appears to move away from the more prescriptive pattern of IEC 60880, and this means that alternative verification and development activities may be introduced.

Where IEC 60880 was previously unclear about precisely which sections or clauses were applicable in different situations, IEC 62566 has gone some way to address this. This is typical of what we would expect from a standard which has been developed more recently.

In the following sections we discuss our results in more detail. When identifying these, we have made the assumption that the differences of interest are those which have an impact on V&V. Where there is a difference between the standards which we consider will not have a significant impact on the V&V activities to be performed, we have not discussed this in detail.

#### 3.4.1 Requirements phase

The requirements phase is dealt with in Section 6 in IEC 60880 and Section 6 in IEC 62566. Although the standards are slightly different, this is not due to the difference in technologies used. More specifically, there are very few significant differences relevant to this phase which impact on V&V activities, with the exception of verification of the requirements specification. Section 6.6 of IEC 62566 requires that a critical analysis of the requirements specification is performed, while IEC 60880 does not. This critical analysis is intended as verification of the requirements specification, and provides an opportunity to identify potential omissions and inconsistencies before design and implementation begins.

We would note that Section 8.1.8 of IEC 60880 does state that the output of each phase of the development lifecycle should be verified, which could be read as a requirement to review and analyse the requirements specification. However, this is less explicit, and we consider that it would be reasonable to expect that less rigorous analyses of requirements may be presented under IEC 60880 than IEC 62566.

#### 3.4.2 Design and implementation phase

Design and implementation is dealt with in Section 7 in IEC 60880 and Section 8 in IEC 62566. There is some divergence in the content of the standards in this section, as we might expect due to the use of design and implementation techniques relevant to the particular technology under consideration. However, not all of these differences impact V&V; those that do are described below.

In terms of design constraints, IEC 60880 is more prescriptive in what must be considered at the design and implementation stage. Specifically, both Section 7.3 and Annex B require that consideration is given to decomposition into modules, use of interrupts, execution time calculations, modification control, coding rules, memory access and so on. If this consideration is not given, then IEC 60880 requires that a justification be provided. In addition IEC 60880 also states in Section 7.2.2 that the choice of language should not prevent the use of certain error-limiting constructs, and provides guidance for the selection of language and tools. This should be contrasted with Section 8.3.4.3 of IEC 62566. This section introduces strongly recommended constraints relating to side-effects, resources, initialization of signals and delays. However, the standard emphasises that these are not mandatory, a declaration which is missing from the constraints given in Section 7.3 of IEC 60880.

In addition, IEC 62566 is more explicit that additional design considerations may apply on a case by case basis, with Section 8.3.4 stating that the design rules should reflect the latest knowledge. That is, IEC 60880 may be interpreted as containing an exhaustive list of all design considerations, while IEC 62566 makes it clearer that the design considerations identified are a representative sample of those which may apply for any given system.

The second area in which the standards differ relates to the use of tools. IEC 60880 requires firstly (Section 7.2) that translators should be thoroughly tested, and in addition to this recommends the use of automated tools and the imposition of further requirements for tool qualification (discussed in this report in Section 3.4.7). By contrast, the design and implementation section of IEC 62566 does not explicitly require the thorough testing of tools – such as those used for synthesis, place and route – if this has already been performed and documented by the supplier of such tools, although it does also impose equivalent requirements to those discussed in this report in Section 3.4.7.

In addition to the requirements placed on tools, the standards differ in what they require to be present in the design documentation. Section 8.3.10 of IEC 62566 is more explicit than the equivalent Section 7.4 of 60880, requiring the description of design decisions pertaining to issues including control flows and data paths, protocols and algorithms, initialization of registers and the memory map. By contrast, IEC 60880 requires only that "sufficient detail" should be provided. This has two potential impacts on the verification and validation activities: firstly, that under IEC 60880 it may be possible to have multiple interpretations of how much detail is sufficient, and secondly that under IEC 62566 the adequacy of the design decisions must be justified – and can therefore be confirmed.

The final area in which the standards differ in this phase is in the extent of V&V that they recommend performing. Although both of them have a dedicated verification section (see Section 3.4.3 in this report), both also discuss V&V activities, to differing extents, in this section.

In Section 7.3, IEC 60880 explicitly requires verification of intermediate design products, which is not required by IEC 62566. We note that this may be implied in the requirement of IEC 62566 that the design should allow easy verification, but this is not equivalent to the explicit requirement that intermediate design products should undergo verification. By contrast, Section 8.7 of IEC 62566 describes a formal review process to be undertaken at the end of the design and implementation phase; this constraint is, however, omitted from IEC 60880. There is a brief mention of a review process in Section 7.4 of IEC 60880, but no equivalent description of the V&V activities to be undertaken during this. The effect of these different requirements is that we may expect different verification artefacts from the design and implementation phase of systems developed under the two standards.

Additionally, Section 8.4.7 of IEC 62566 explicitly requires static timing analysis to be performed, for which no equivalent requirement is found in IEC 60880. Correspondingly, it would be expected that verification of best and worst case time – amongst other properties – has been performed for systems developed under IEC 62566, but not necessarily for those under IEC 60880.

#### 3.4.3 Verification

Verification of software and HPDs is dealt with in Section 8 of IEC 60880 and Section 9 of IEC 62566 respectively. Although these sections are relatively extensive, there are only a few significant differences between the two standards in this phase.

The first difference relates to the scope of verification, with particular reference to the use of pre-developed items. Section 9.3 of IEC 62566 identifies that part of the role of verification is to assess pre-developed products against the rules specified by their

suppliers, and the requirements of Section 7 (dealing specifically with pre-developed items, and covered in this report in Section 3.4.8). By contrast, although Section 8.2.3.3 of IEC 60880 also requires that the requirements of Section 15 (dealing specifically with pre-developed items, and covered in this report in Section 3.4.8) are met, there is no equivalent requirement that pre-developed items should be assessed against rules specified by their suppliers. The effect of this omission is a slightly different scope in the V&V activities required by each standard. Furthermore, Section 9.1 of IEC 62566 identifies a requirement to confirm the adequacy of selection of pre-developed items, and of such items with their component requirement specification. That is, the use of pre-developed items must be justified, and shown to be necessary within the wider system. These differences should be taken into account when considering the implications of IEC 62566 Section 7 vs IEC 60880 Section 15 on verification of pre-developed items (as we do in this report in Section 3.4.8).

Secondly, we have already seen that the two standards differ in the extent to which they explicitly describe the content of documentation. IEC 60880 is more prescriptive about the documentation to be produced during verification, requiring a distinct software test specification, test report and design verification report. It is also quite specific about the information to be included in each of these, requiring for example that the test specification includes test environment, test procedures, acceptance criteria and so forth. By contrast, IEC 62566 does require that tests, goals, expected results, acceptance criteria, inputs and outputs etc. should be recorded, but does not constrain the type of documentation to be produced (e.g. test specification, test report). Although the two standards do require the same rigour of documentation in the verification phase, it is important to be aware that this documentation may be presented differently under the two standards.

In addition, IEC 62566 places much more emphasis on automation of tests, requiring tests to be fully automated and any manual input or observation justified (as these are considered potentially error-prone). IEC 60880, by contrast, permits automated code analysis but does not require manual analysis to be justified.

Finally, with reference to the actual activities performed during V&V, IEC 62566 is slightly more prescriptive in terms of identifying the verification activities which must be performed (for example, static verification activities such as type / syntax checking, parameter checking, OOR checking and dead state detection). By contrast, IEC 60880 provides an informative annex detailing potential verification activities including program analysis, program proving, path testing, data movement testing. However, because these are informative only, their selection must be on a case-by-case basis, unlike the mandatory activities prescribed by IEC 62566.

#### 3.4.4 Software / HPD aspects of system integration

Software and HPD aspects of system integration are dealt with in Section 9 of IEC 60880 and Section 10 of IEC 62566. There are no significant differences which impact V&V, with the only exception being that IEC 62566 explicitly requires that verification software tools should be compliant with its requirements on software tools for development (Section 15 of IEC 62566, which is detailed in this report in Section 3.4.7). IEC 60880 does not explicitly require this, so should any software tools be used for verification then this may be an area where further work could be merited.

#### 3.4.5 Software / HPD aspects of system validation

Software and HPD aspects of system validation are dealt with in Section 10 of IEC 60880 and Section 11 of IEC 62566. As above, there are no significant differences to discuss, with the exception of a slightly more stringent constraint on the equipment used for calibration. IEC 60880 requires that this be demonstrated to be suited to the purpose of system validation, while IEC 62566 does not require this. However, this is unlikely to have a significant impact on V&V activities.

The only other area of difference in this phase relates to the documentation. Section 10.3 of 60880 identifies that software tools used in the validation process should be documented as an item in the validation report. The corresponding section dealing with validation reports in IEC 62566, Section 11.4, does not mention this, although it is included in IEC 61513. There is unlikely to be any significant impact on verification and validation, but this omission from IEC 62566 may be an indication that information on software tools for validation could potentially be missing.

#### 3.4.6 Modification

Software and HPD modification is covered in Section 11 of IEC 60880 and Section 12 of IEC 62566. There are no significant differences between the two standards in terms of verification and validation activities.

#### 3.4.7 Software tools for development

The use of software tools for development is addressed in Section 14 of IEC 60880 and Section 15 of IEC 62566. There are no significant differences to discuss; indeed, IEC 62566 explicitly requires conformance with IEC 60880 with the exception of a small number of constraints specific to microprocessors. It also adds some HPD-specific requirements around tools for logic synthesis, HDL source statements, command-line arguments

#### 3.4.8 Acceptance of pre-developed products

The acceptance process for pre-developed products is considered in Section 15 of IEC 60880 (and configuration of these in Section 7.1.4), and in Section 7 of IEC 62566.

One area in which the two standards differ, and which can have a significant impact on verification and validation, is in the evaluation of the quality of the pre-developed product. IEC 62566 allows more scope for interpretation in the ways in which the quality of the product could be demonstrated. In particular, Section 15.3.2 of IEC 60880 explicitly identifies the documentation that we should expect to be made available. This includes the software quality plan, the specification documents, the software / hardware integration plan, the validation plan and the results of verification and validation. By contrast, IEC 62566 requires only that a documentation review is carried out on the design and verification documents of the pre-developed product. This difference can be partly attributed to the fact that pre-developed products - such as IP cores – for use in FPGA-based systems may not be provided with all of the specific documentation discussed in IEC 60880; that is, the information may be present, but provided in a different form.

Furthermore, IEC 60880 imposes a further quality requirement, that the development of the pre-developed product should have been in accordance with the annexes of IEC

60880 itself. IEC 62566 does not impose an equivalent requirement. However, it is worth nothing that the programming process for blank integrated circuits is required to be "fault free".

The other area in which IEC 62566 and IEC 60880 differ is in the scope for, and constraints placed on, the use of operating experience when assessing a pre-developed product. In general, IEC 62566 allows more scope for interpretation in the ways in which operating experience can be used, with Section 7.4.3 stating that it may be used to compensate for limited documentation weaknesses regarding reliability or design. By contrast, Section 15.3.3.2 of IEC 60880 is explicit that operating experience can never completely replace documentation evaluation. IEC 60880 is also more specific about the weaknesses in design that can be compensated for with operating experience.

By contrast, however, IEC 62566 is more specific about the conditions under which operating experience can be considered valid, with Section 7.4.3 requiring "equivalent" conditions. IEC 60880, in Section 15.3.3.1 requires "similar" conditions. As there is no further information given about the ways in which the conditions must be similar, IEC 60880 has the potential for multiple differing interpretations when determining the validity of operating experience.

#### 3.5 CONCLUSIONS

Overall, we have found very few indications of significant differences impacting on V&V between IEC 60880 and IEC 62566, at any stage of the development lifecycle.

In general, IEC 62566 is less prescriptive about the specific documents that need to be produced. In some cases IEC 62566 has clarified requirements in IEC 60880, resulting in a greater specificity in these clauses. As above, these clarifications have typically not taken the form of requiring that specific activities be performed, but have rather been clarifications that, for example, the constraints of a particular clause either in IEC 62566 or in another standard are applicable in situations which were previously ambiguous.

# 4 Behavioural properties

In the safety triangle of justification, consideration of the behavioural properties aims to show that the expected behaviour of the system or component is met. Typically, this is organised under attribute headings such as functionality, timing and accuracy. This typically requires the use of a number of V&V techniques. Different properties (or attributes) can be considered for different types of systems or components. The exact set of attributes to be considered would need to be defined for each system.

Therefore, in assessing the usefulness of a particular technique, it is necessary to consider

- the contribution of the behavioural attribute to the overall case

- the contribution of the V&V technique to establishing the behavioural attribute

- the inputs required to apply the V&V technique

The combination of all the techniques deployed for each behavioural attribute generates a level of confidence that the behaviour of the complete system is well understood and correctly implemented. In selecting appropriate V&V techniques, the most productive are those that provide a high level of assurance but require modest amounts of effort, while the least attractive provide little assurance and involve large amounts of effort. The position of a technique on the spectrum depends on the nature and structure of the application being assessed. In this section, for common groupings of behavioural attributes, we compare how V&V techniques vary between microprocessor and FPGA based systems, with particular emphasis on those areas where the V&V required for one architecture gives significantly more confidence or requires significantly less effort than another.

#### 4.1 FUNCTIONALITY

The V&V of a system's functionality refers to the correct implementation of the defined system functions. One type of functionality involves specifying the existence of a facility or capability of the system: for example, an instrument measuring temperature may specify that the user be able to calibrate sensor X using some particular kind of data set, perhaps over a particular interface. A part of the specification of the functionality of the system can also involve prescribing an algorithm or properties of an algorithm used to calculate some quantity in the system.

| V&V area                                 | Microprocessor V&V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | FPGA V&V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Code inspection                          | Code inspection of code written in<br>a high level language can reveal the<br>logical intent of well-structured<br>single-threaded code, but by<br>suggesting structures, may lead the<br>reviewer into making the same<br>logical errors as the developer.<br>Concurrent functional<br>requirements are difficult to<br>analyse using code review without<br>tool support, particularly as it may<br>not be obvious that another<br>function implemented elsewhere in<br>the code may interact with shared<br>resources such as global variables.<br><b>Effectiveness/cost</b><br>Low cost, reasonable confidence if | Code inspection of HDL can produce<br>less confidence than the equivalent<br>activity for microprocessor code<br>because hardware implementation<br>details are exposed, and HDL designs<br>are inherently more concurrent. It may<br>be more useful to concentrate on code<br>review at the ESL level rather than at<br>executable HDL level, although<br>subsequent coverage of potential<br>issues that are created at HDL level<br>only depends on the means by which<br>the HDL is generated. A summary of<br>the development flow can be found in<br>Appendix B.<br><b>Effectiveness/cost</b><br>Low cost, less confidence than |  |

|                                          | code is well structured and<br>commented with limited<br>concurrent behaviour or assembly<br>code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | microprocessor, especially if review<br>confined to low level HDL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Random testing,<br>functional<br>testing | These techniques are similarly applicable to both microprocessors and FPGAs.<br><b>Effectiveness/cost</b><br>Relatively low cost. The effectiveness of testing is heavily dependent on the<br>linkage between a test profile and the specific claims supported by the<br>results.                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| V&V area               | Microprocessor V&V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FPGA V&V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Formal<br>verification | Static analysis using a tool such as<br>Malpas or Frama-C produces a<br>deductive proof that a piece of<br>code has a behaviour that is stated<br>in a formal specification language.<br>The effectiveness of the technique<br>depends on the identification of<br>significant functions and correct<br>translation of their natural<br>language requirements into<br>mathematical definitions of<br>behaviours. Depending on the<br>extent of the properties proved,<br>levels of confidence can be high.<br>Tools require qualification, and<br>those that need extensive manual<br>intervention to link deductions<br>together may introduce<br>opportunities for error.<br><b>Effectiveness/cost</b><br>Depending on the functional<br>properties verified, static analysis is<br>time consuming but is considered<br>to produces the highest practical<br>levels of confidence in the<br>functional correctness of code.<br>Tools range in cost from free to<br>expensive. | Assertion languages (which can<br>sometimes be part of an HDL) enable<br>statements to be written about the<br>behaviour of a piece of HDL code,<br>which can be checked by simulation or<br>deductive means using a range of<br>tools. However, the low level nature of<br>these assertions can make it difficult to<br>frame high level functional properties.<br>Verification tools at ESL/TLM level<br>address functionality more fully, but<br>tend to work by simulation rather than<br>deductive means, as the complexity of<br>ESL language complexity does not<br>easily facilitate deductive proof.<br>Simulation cannot typically provide<br>complete coverage of a state space in<br>systems of more than trivial<br>complexity, although there are<br>established techniques available to<br>gain confidence that a given level of<br>coverage has been achieved.<br><b>Effectiveness/cost</b><br>HDL verification tools can be<br>expensive, even on a subscription<br>basis. These tools are generally closed<br>source, but have long development<br>pedigrees and wide use in industry.<br>The level of confidence that can be<br>obtained through using these tools at a<br>low level for <i>functional</i> (as opposed to<br>integrity) properties is not particularly<br>high, but their use is mandated by<br>IEC 62566. Some HDL verification tools<br>provide assertion generators or check<br>that assertions cover particular<br>properties, but these tools cannot<br>infer the designer's intention about<br>what the code is supposed to do. HDL<br>assertion checking is a technique<br>better suited to addressing<br>vulnerabilities in designing code for<br>FPGAs, so we return to it in Section 5. |

| Model checking         | Model checking techniques use a high level representation of a design in a language such as Promela and check properties of interactions between functional blocks and state transitions at a high level. In both the case of microprocessor and FPGAs, some element of skill and discretion is needed in manually constructing a suitable model. It is time-consuming and expensive task, although many common tools are free or open source.<br><b>Effectiveness/cost</b><br>In each case, the strength of the conclusions with reference to the model being checked is high, but is limited in the context of the actual implementation it is modelling by constraints on the confidence in the equivalence of the models to the implementation in question. Model checking is labour-intensive and expensive.                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 1: Functionality V&V

#### 4.2 TIMING

Timing behaviour has different facets depending on whether we are considering

- low-level hardware concerns such as propagation of signals and rise times of particular transistor technologies

- length of time for a particular clocked processor to work through a compiled algorithm written in a high level programming language

- latency of a real time signal processing pipeline or response time to an asynchronously presented demand

Some of these concerns apply predominantly to microprocessor based implementations, while some apply to HDL implementations. Functional level testing techniques apply to both. These issues are presented in Table 2 and elaborated in the sections that follow.

| V&V area                                        | Microprocessor V&V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FPGA V&V                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Worst case<br>execution time<br>analysis (WCET) | We describe the issues<br>involved in worst case<br>execution time analysis<br>in Section 4.2.1.<br><b>Effectiveness/cost</b><br>WCET analysis can give<br>high levels of<br>confidence in adequate<br>timing performance of<br>an algorithm<br>implementation, but it<br>is an expensive activity,<br>often requiring manual<br>intervention that is<br>frequently intractable,<br>in which case<br>approximations can be<br>used (which give a<br>reduced level of<br>confidence compared<br>with an analytical<br>solution). | Although not directly applicable as WCET<br>analysis is a technique used for microprocessor<br>code, HDL program code can nevertheless be<br>written in a paradigm in which data flows round<br>a (spatial) loop several times, and after some<br>number of iterations emerges into a different<br>part of a data processing pipeline. It is<br>important to ensure that this kind of hidden but<br>semantically significant construction is not<br>neglected in HDL verification. |

| V&V area                              | Microprocessor V&V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FPGA V&V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V&V area<br>Static timing<br>analysis | Microprocessor V&V<br>For a microprocessor,<br>verification of timing<br>properties at the HDL<br>physical levels takes<br>place when the<br>microprocessor is<br>designed and verified by<br>the manufacturer. The<br>programmer writing<br>code for a<br>microprocessor should<br>address WCET and<br>performance issues, but<br>does not need to be<br>concerned with<br>propagation or other<br>electronic issues: the<br>microprocessor<br>programmer's model of<br>hardware is a discrete<br>abstraction. | <b>FPGA V&amp;V</b><br>Background to static timing analysis is given in<br>Section 4.2.2. Static timing analysis is important<br>in order to check that synchronous timing<br>constraints that are implicit at HDL level are not<br>violated during place-and-route. It is an<br>automated process supported by a wide variety<br>of tools. So called "back annotations" imposing<br>extra constraints on the HDL as a result of how<br>that HDL has been synthesised and placed onto<br>the FPGA can result in a cyclic FPGA<br>development process, where multiple revisions<br>may be necessary before an acceptable<br>bitstream is produced. However, this is not so<br>different from the case with a microprocessor,<br>where a design might not necessarily fit into<br>memory or within the timing constraints of the<br>application after a first pass. Similarly, with a<br>microprocessor, some elements of the analysis<br>of high level code or synchronous HDL can be<br>applied independently of a particular<br>microprocessor or FPGA, while issues such as<br>place-and-route that are dependent on a<br>particular FPGA are analogous in difficulties<br>encountered when a traditional piece of code is<br>compiled for a different microprocessor.<br>However, in the case of a microprocessor, the<br>extra WCET analysis that would be required for<br>a microprocessor based design would be a<br>larger task than rerunning an automatic static<br>timing analysis for an FPGA. While static timing<br>analysis is typically only part of rigorous<br>developers of FPGA-based solutions, WCET<br>analysis is typically only part of rigorous<br>development processes.<br><b>Effectiveness/cost</b><br>Static timing analysis should not pose a<br>significant extra difficulty unless a design is<br>being targeted onto an FPGA that is not large or<br>fast enough to accommodate the high level<br>design. Reliance on complex closed source<br>toolchain may have a small negative impact on<br>confidence when compared to a<br>microprocessor, an FPGA <i>chip</i> design must be<br>verified, so the verification of the HDL for the<br>programmable part of the FPGA is an extra step<br>with opportunities for bugs or inaccuracies.<br>Since static timi |

| V&V area                                                                                                                           | Microprocessor V&V                                                                                                                                                                                                                                                                                                                                                                                                                                        | FPGA V&V                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Time response test                                                                                                                 | This is a generic technique for asynchronous applications. At this level,<br>timing properties are dictated by communications protocols or plant need.<br>For example, real time protocols can require responses within a fixed<br>interval, while a plant need might specify a maximum time that should<br>elapse between a detectable set of plant conditions and a control or safety<br>response, such as an alarm annunciation.<br>Effectiveness/cost |                                                                                                                                                                                                                                                           |

| These techniques are inexper<br>although this is dependent or<br>the tests over inputs and envi<br>This can be more difficult in t |                                                                                                                                                                                                                                                                                                                                                                                                                                                           | pensive and give reasonable levels of confidence,<br>t on arguing that there is adequate coverage of<br>environments to which timing might be sensitive.<br>in the microprocessor case, where operating<br>een concurrent tasks often produce intractable |

Table 2: Timing V&V

#### 4.2.1 Worst case execution time

Most programming languages used in the development of I&C systems are imperative languages. This means that they set up a set of variables with state, and consist of sequential *statements* that modify that state. (The allocation of variables that form part of the notional state at any one time changes as functions are entered and exited, but this can be overlooked for the sake of the current discussion.) Some statements contain logical tests, such that the next statement to be executed may be determined by the value of some data in a variable. There is an infinite number of ways<sup>1</sup> of implementing an algorithm defined by an application in imperative code. Each different way of implementing the algorithm may give rise to a different number of statements that must be executed until the eventual result is computed; this number of statements will usually change, depending on the values of the input data to a given algorithm. The system of state transitions is discrete: each transition is notionally instantaneous, and any execution history always contains a whole number of executed statements. However, each of these transitions cannot in practice be instantaneous, so a given algorithm takes a finite amount of time to complete. The worst case execution time (WCET) is determined by whichever input data produces an execution with the largest number of statements. The more transitions, the longer this time will be. The state transitions corresponding to this timescale of sequential C statements does not have a straightforward relationship to physical time. This is because different statements will be converted into different sequences of microprocessor instructions by different compilers, and different microprocessor instructions take different numbers of physical clock cycles to complete. Instruction retries and processor optimisations such as pipelining, out-of-order execution and asynchronous communications with external ICs over system buses can even make the length of time needed to process an instruction non-deterministic.

In themselves, these factors make WCET analysis a complex task that involves consideration of interactions between high level language, compiler and microprocessor. It is made even harder when an operating system is used, or where function invocation is driven by asynchronous interrupts, because function execution can be arbitrarily interrupted by other parts of a system, which can result in complex mutual dependencies or reliance on unbounded external stimuli, which can result in an analytically intractable implementation. Where bounds can be found, they are often

<sup>&</sup>lt;sup>1</sup> though a finite number of *good* ways